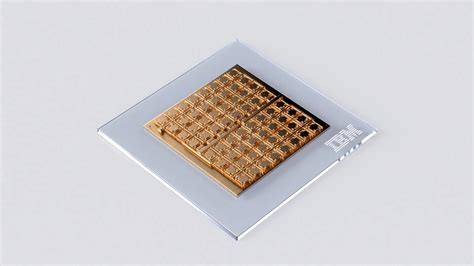

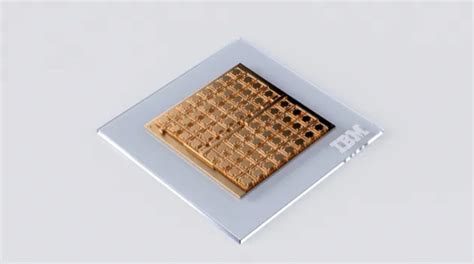

ibm hermes chip | IBM Research Inference Chip Performance Results Released ibm hermes chip We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM). Las Vegas Nevada's best FREE dating site! 100% Free Online Dating for Las Vegas Nevada Singles at Mingle2.com. Our free personal ads are full of single women and men in Las Vegas Nevada looking for serious relationships, a little online flirtation, or .

0 · IBM develops a new 64

1 · IBM Touts Analog

2 · IBM Research Inference Chip Performance Results Released

3 · HERMES Core – A 14nm CMOS and PCM

4 · HERMES Core

5 · HERMES

6 · Analogue in

7 · A 64

Find helpful customer reviews and review ratings for FnS Fountain Pro WA-345-LV Pump at Amazon.com. Read honest and unbiased product reviews from our users.

We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM).

A novel frequency-linearization technique for CCOs is introduced, leading to accurate on-chip matrix-vector-multiply (MVM) when operating over 1 GHz. Measured classification accuracies . IBM's recently published research paper on an analog-digital hybrid chip promises to allow for AI inferencing that's much more power-efficient than fully-digital chips such as the . In the latest issue of Nature Electronics, IBM researchers describe the design and operation of Hermes, an inference chip with 4 million weights and 64 cores that was first .

To address those challenges, we present the IBM HERMES Project Chip: a 64-core AIMC chip based on back-end integrated PCM in a 14-nm CMOS process. The chip delivers . Researchers at IBM Research Europe recently developed a new 64-core mixed-signal in-memory computing chip based on phase-change memory devices that could better .We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM). It compris.We present a 256 × 256 in-memory compute (IMC) core designed and fabricated in 14-nm CMOS technology with backend-integrated multi-level phase change memory (PCM).

IBM introduces the IBM HERMES project chip: a fully integrated in-memory compute chip comprising 64 analogue in-memory computing cores, digital processing units and an on-chip . In this Article, we report the IBM HERMES project chip: a 64-core AIMC chip based on backend-integrated PCM in a 14 nm complementary metal–oxide–semiconductor process.We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM).

A novel frequency-linearization technique for CCOs is introduced, leading to accurate on-chip matrix-vector-multiply (MVM) when operating over 1 GHz. Measured classification accuracies on MNIST and CIFAR-10 datasets are presented when two cores are employed for . IBM's recently published research paper on an analog-digital hybrid chip promises to allow for AI inferencing that's much more power-efficient than fully-digital chips such as the current. In the latest issue of Nature Electronics, IBM researchers describe the design and operation of Hermes, an inference chip with 4 million weights and 64 cores that was first fabricated last year. To address those challenges, we present the IBM HERMES Project Chip: a 64-core AIMC chip based on back-end integrated PCM in a 14-nm CMOS process. The chip delivers simultaneously four key advances over the previous implementations dis-cussed above.

Researchers at IBM Research Europe recently developed a new 64-core mixed-signal in-memory computing chip based on phase-change memory devices that could better support the computations of deep neural networks.

We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM). It compris.We present a 256 × 256 in-memory compute (IMC) core designed and fabricated in 14-nm CMOS technology with backend-integrated multi-level phase change memory (PCM).IBM introduces the IBM HERMES project chip: a fully integrated in-memory compute chip comprising 64 analogue in-memory computing cores, digital processing units and an on-chip communication network.

IBM develops a new 64

In this Article, we report the IBM HERMES project chip: a 64-core AIMC chip based on backend-integrated PCM in a 14 nm complementary metal–oxide–semiconductor process.We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM).

A novel frequency-linearization technique for CCOs is introduced, leading to accurate on-chip matrix-vector-multiply (MVM) when operating over 1 GHz. Measured classification accuracies on MNIST and CIFAR-10 datasets are presented when two cores are employed for .

IBM's recently published research paper on an analog-digital hybrid chip promises to allow for AI inferencing that's much more power-efficient than fully-digital chips such as the current. In the latest issue of Nature Electronics, IBM researchers describe the design and operation of Hermes, an inference chip with 4 million weights and 64 cores that was first fabricated last year. To address those challenges, we present the IBM HERMES Project Chip: a 64-core AIMC chip based on back-end integrated PCM in a 14-nm CMOS process. The chip delivers simultaneously four key advances over the previous implementations dis-cussed above.

Researchers at IBM Research Europe recently developed a new 64-core mixed-signal in-memory computing chip based on phase-change memory devices that could better support the computations of deep neural networks.We present a 256×256 in-memory compute (IMC) core designed and fabricated in 14nm CMOS with backend-integrated multi-level phase-change memory (PCM). It compris.We present a 256 × 256 in-memory compute (IMC) core designed and fabricated in 14-nm CMOS technology with backend-integrated multi-level phase change memory (PCM).

IBM Touts Analog

peep toes prada

prada 2 punjabi song mp3 download

IBM Research Inference Chip Performance Results Released

Reserve Polo Towers parking through SpotHero. Find, book & save on parking using SpotHero with convenient garages, lots & valets near your destination.Las Vegas Barber Expo 2019 Where & When. Location: Las Vegas, NV 89183. Event Date: 2019/09/29 09:00:00 AM (Sunday) Categories: Speed Fade. Fade and Beard. Lady Barber. Traditional. Free Style.

ibm hermes chip|IBM Research Inference Chip Performance Results Released